CMOS反相器電路解析

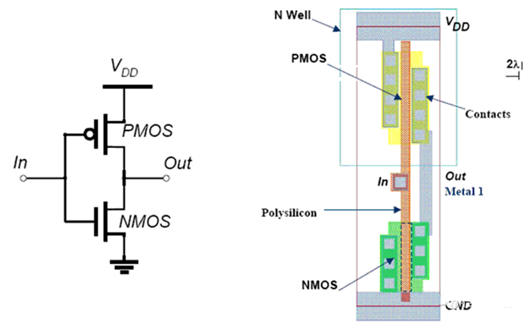

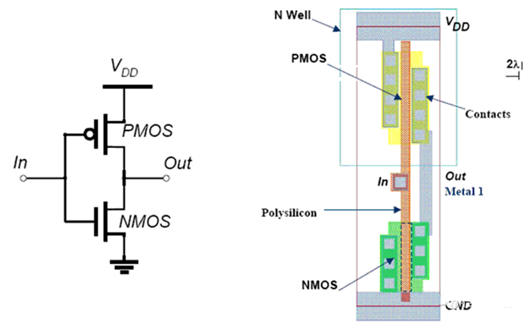

一、電路原理圖與物理版圖

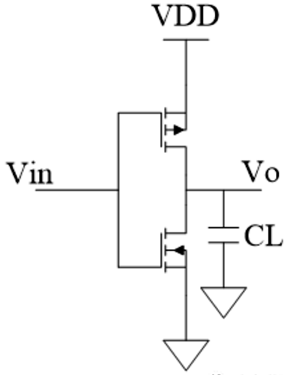

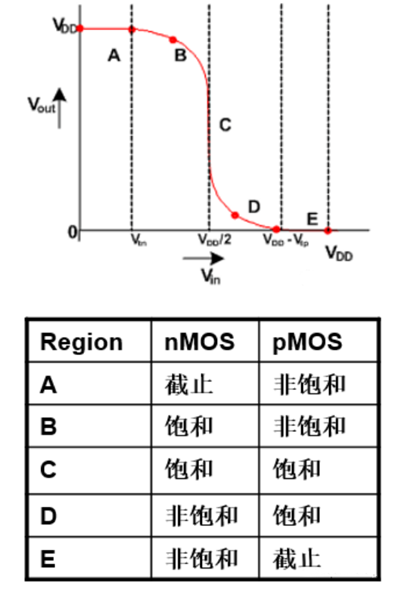

CMOS反相器由NMOS和PMOS晶體管組成,其電路原理圖和物理版圖如下圖所示。物理版圖相當于MASK圖形,集成電路制造基于此圖形,經光刻、生長、注入等工藝逐層實現。因此,任何電路圖最終需轉換為物理版圖供生產。

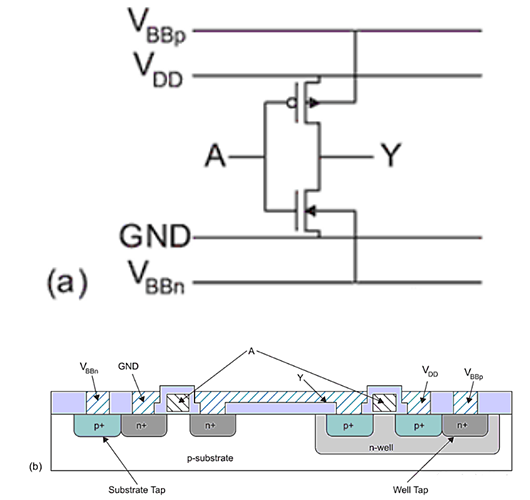

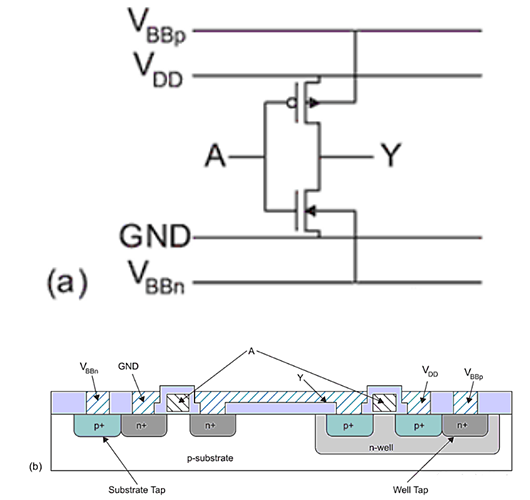

CMOS反相器實際剖面圖如下,展示了其層疊結構。

通常,VDD與VBBp連接且接至VDD,作為PMOS的源端;VBBn與GND連接并接地,充當NMOS的源端。隨著工藝尺寸縮小,為節省面積,VBBp和VBBn不再與每一門電路的VDD和GND連接,而是每隔幾個電路連接一次。不過,這會導致襯底偏置電壓(VBS)與源端出現minor電壓差,進而改變閾值電壓VT。VBS與VT呈反比關系:VBS越大,VT越小;VBS越小,VT越大。

對于數字集成電路工程師而言,了解襯底偏置電壓對VT的影響即可。在先進工藝中,為實現低功耗設計,BodyBiasingGenerator(BBG)可微調偏置電壓,在功耗與性能間做出權衡。降低VT能提升性能,但會增加漏電;提高VT可減少漏電,但對性能有負面影響。

二、電路分析

(一)電路組成與負載電容

CMOS反相器電路包含一個負載電容CL。對于CMOS門電路,其輸出需驅動負載。一般而言,CMOS門電路的負載是金屬連線與地之間的電容以及下一級電路輸入柵極與地之間的電容。由于MOSFET是電壓控制電流器件,僅靠電流無法實現邏輯傳遞。負載電容在充電和放電過程中,使其節點在VDD和地電勢間跳變,從而傳遞邏輯數值。

(二)反相器轉移特性曲線

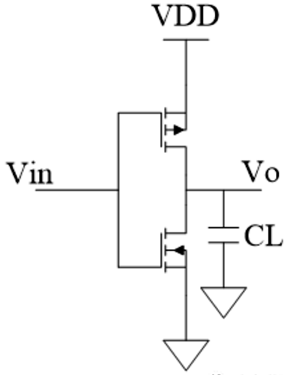

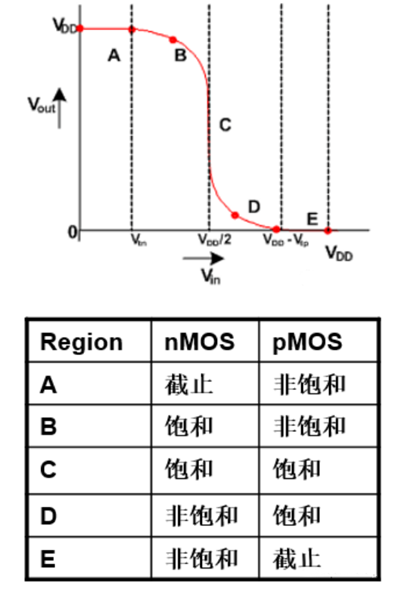

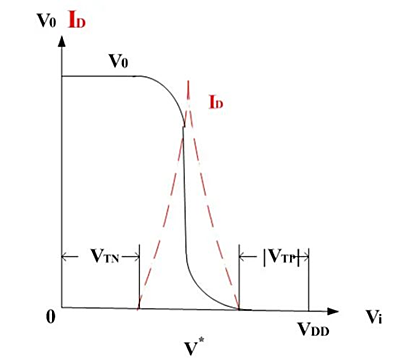

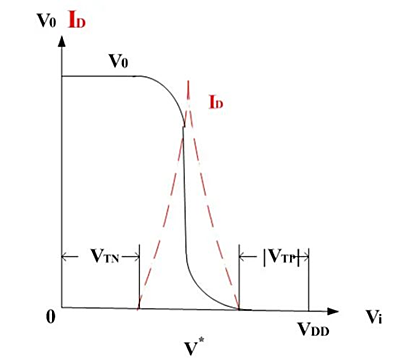

假設PMOS和NMOS的VT值相同,輸入電壓變化引起的輸出電壓變化曲線(反相器轉移特性曲線)如下:

A區域:當輸入電壓Vin在0V到VTN之間時,NMOS截止,PMOS處于非飽和狀態,但無電流通路,因此無電流流過,輸出電壓保持不變。

B區域:Vin在VTN到1/2VDD之間時,NMOS處于飽和狀態,PMOS處于非飽和狀態。由于PMOS的VDS不大,電流較小,電容放電速度較慢。

C區域:當Vin在1/2VDD附近時,NMOS和PMOS同時處于飽和狀態,放電速度突然增大。此時,PMOS很快達到飽和狀態(VDS增加),而NMOS很快達到非飽和狀態(VDS減少),隨后進入D區域。

D區域:Vin在1/2VDD到接近(VDD-VTP)的區間時,NMOS處于非飽和狀態,PMOS處于飽和狀態。由于NMOS的VDS不大,電流較小,電容放電速度較慢。

E區域:當Vin大于VDD-VTP時,PMOS截止,無電流通路,輸出電壓固定在0V。

從上述特性可見,輸入電壓為VDD時,輸出電壓為0V;輸入電壓為0V時,輸出電壓為VDD,滿足反相器的邏輯關系。

(三)輸入電壓與電路電流的關系

分析表明,當輸入電壓小于NMOS的VT或大于VDD-|VTP|時,電路幾乎不產生電流。僅在中間區間,才會產生較大電流,尤其當兩個管子均處于飽和狀態時。這種特性意味著電路在不發生狀態翻轉時幾乎不消耗電流,而一旦發生翻轉,借助NMOS和PMOS的互補性,可迅速實現狀態轉換,進而提升電路性能。

通過以上分析,深入理解CMOS反相器的電路原理和特性,有助于在數字集成電路設計中更好地運用和優化反相器,以實現高性能、低功耗的電路設計。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280